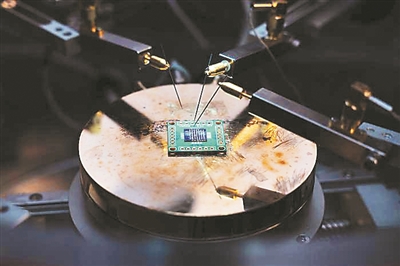

科学家在半导体晶体管堆叠方面取得了突破性进展。图片来源:沙特阿卜杜拉国王科技大学

沙特阿卜杜拉国王科技大学研究人员在微芯片设计领域创下新纪录,成功研制出全球首个面向大面积电子器件的6层堆叠式混合互补金属氧化物半导体(CMOS)芯片。此前公开报道的混合CMOS堆叠层数从未超过两层,这一突破标志着芯片集成密度与能效迈上新台阶,有助电子设备的小型化和性能提升。

CMOS芯片几乎存在于所有电子设备中,从手机、电视到卫星和医疗仪器。与传统硅基芯片相比,混合CMOS芯片在大面积电子领域更具优势,有望在柔性电子、智慧医疗和物联网等领域发挥重要作用。

长期以来,半导体行业一直依靠缩小晶体管尺寸来提高集成密度,但已接近量子力学的极限,同时成本也在急剧上升。要继续推进芯片性能,必须走出平面扩展的思路,垂直堆叠晶体管是最具潜力的方向之一。

芯片多层堆叠的最大挑战在于制造温度。常规工艺往往需要几百摄氏度的高温,这在添加新层时可能会损坏下层结构。而新方法中,所有工艺步骤的温度均未超过150℃,多数步骤甚至接近室温完成,显著降低了材料受损风险。

此外,层与层之间的表面必须尽可能光滑。新设计中改进了工艺,使表面平整度优于以往。而在垂直堆叠中,层间精确对准尤为重要,研究团队也在这方面显著优化了制造流程。

在微芯片设计中,核心目标就是在更小的空间里实现更高性能。此次研究通过优化多个关键步骤,为垂直扩展与功能密度的进一步提升提供了一条可行路径。